1.Jurnal[kembali]

2. Alat dan Bahan[kembali]

A. Alat

1. Jumper

2. Panel DL 220D

3. Panel DL 2203C

4. Panel DL 2203S

B. Pada Proteus

3. Rangkaian [kembali]

4. Prinsip Kerja [kembali]

jadi rangkaian tersebut terdapat rangkaian J-K Flip Flop dan D Flip Flop dengan ketentuan B0=1, B1=1, B2=1, B3=clock, B4=1, B5=tidak dihubungkan, B6=tidak dihubungkan.

Flip flop merupakan rangkaian elektronika yang memiliki dua kondisi stabil dan dapat digunakan untuk menyimpan informasi.

1. D-Flip Flop

D Flip-flop merupakan salah satu jenis flip-flop yang dibangun dengan menggunakan flip-flop R-S. Namun pada D Flip-flop inputan R diberi gerbang NOT.

Arus mengalir dari power ke B1 dan ke kaki set. Arus mengalir ke B0 dan ke input R. Pada bagian D dan CLK tidak berlogika 1 maupun 0 karena tidak dihubungkan dan ini disebut juga dengan kondisi dont care dan tidak memberi pengaruh ke output.

2. J K-Flip Flop

J-K Flip-flop merupakan flipflop yang tidak memiliki kondisi terlarang atau yanng berarti diberi berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluaran atau outputnya.

Pada rangkaian, vcc terhubung ke B1 yang berlogika 1 lalu terhubung ke set. lalu arus mengalir ke B2 yang berlogika 1 lalu ke J. lalu terdapat inputan clock yang terhubung ke clk. arus mengalir ke B4 yang berlogika 1 ke K. dan arus mengalir ke B0 yang berlogika 1 ke R.

Karena J dan K ini berlogika 1, yang mana inputan ini aktif (karena bersifat active high) maka akan meghasilkan kondisi togel, disini juga terdapat CLK yang mana memberi pengaruh untuk active low yang mana akan menggantikan hasil output saat berlogika 1 ke 0 .

untuk S dan R, pada dasarnya R ini membuat outputnya menjadi berlogika 0 dan S membuat outputnya itu menjadi berlogika 1. Pada rangkaian, R dan S bersifat active low yang mana rangkaian tersebut akan aktif jika inputnya 0. Namun pada rangkaian di atas R dan S ini berlogika 1, ini berarti R dan S ini bersifat tidak aktif.

5. Video Percobaan [kembali]

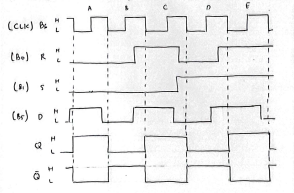

1. Analisa apa yang terjadi saat input B3 dan B2 dihubungkan ke clock dan K berlogika 1. Gambarkan timing diagramnya!

jawab :

Kondisi yang dianalisa ialah saat S dan R tidak aktif. Sehingga input J dan K lah yang mempengaruhi output Q dan Q'. seperti yang diketahui input b3 dan b2 dihubungkan ke clock dimana nilainya berubah-berubah dari 0 ke 1 ( kondisi risetime). Berdasarkan tabel kebenaran saat J=0 dan K=1 maka outputnya Q=0 dan Q'=1

jawab :

kondisi pada rangkaian ialah saat R dan S nya tidak aktif dan D memiliki input clock. ini membuat nilai D aktif maka input D tidak akan mempengaruhi output yang akan muncul. pada tabel kebenaran, nilai D=0 maka nilai Q=0, dan Q'=1. Dan jika D=1 maka Q=1 dan Q'=0

1. Analisa apa yang terjadi saat input B3 dan B2 dihubungkan ke clock dan K berlogika 1. Gambarkan timing diagramnya!

jawab :

Kondisi yang dianalisa ialah saat S dan R tidak aktif. Sehingga input J dan K lah yang mempengaruhi output Q dan Q'. seperti yang diketahui input b3 dan b2 dihubungkan ke clock dimana nilainya berubah-berubah dari 0 ke 1 ( kondisi risetime). Berdasarkan tabel kebenaran saat J=0 dan K=1 maka outputnya Q=0 dan Q'=1

jawab :

kondisi pada rangkaian ialah saat R dan S nya tidak aktif dan D memiliki input clock. ini membuat nilai D aktif maka input D tidak akan mempengaruhi output yang akan muncul. pada tabel kebenaran, nilai D=0 maka nilai Q=0, dan Q'=1. Dan jika D=1 maka Q=1 dan Q'=0

7. Download[kembali]

File Rangkaian [Klik]

HTML File [Klik]

Download Vidio [ klik ]

Data sheet 74LS112 [di sini ]

Datasheet 7474 [di sini]

Datasheet LogicProbe [di sini]

Datasheet SW-SPDT [di sini]

Download datasheet J-K flip flop [ Klik Disini ]

Download datasheet D flip flop [ Klik Disini ]

Tidak ada komentar:

Posting Komentar